In this small project, I wanted to design an RF amplifier from scratch. Of course, the simplest solution is to use an off-the-shelf MMIC that implements the bias network and impedance matching, but that offers a very limited learning experience. Therefore, I decided to design a single-stage class A amplifier around a popular BFR92 VHF/UHF bipolar transistor.

The center design frequency was chosen as 433 MHz because I expect this amplifier to cover both the ISM band and the 70 cm amateur radio band. Additionally, at the time of designing this amplifier, I was also working on two projects that could make use of an amplifier tuned around that frequency. Since the wavelength is much longer than any SMD component, the lumped model and discrete LC components were used. It was also expected that the LC values would be within the range of possible SMD components (not smaller than 1 pF for example). I wanted to achieve more than 16 dB of gain, something that is possible with a single BFR92 transistor. What was more important in this design was minimal reflection from the input and the output. This is because I wanted to use this amplifier before a mixer or after an intermediate frequency filter. Mixers can be sensitive to back reflection, so good return loss is always a plus.

The first version of the amplifier had a characteristics shifted to a lower frequency. By calculating the difference and retuning the amplifier in AWR by said difference, I made a second version. The results in the above figures come from that second version of the retuned amplifier. As can be seen, the return loss has its global minimum almost exactly at the desired 433 MHz. The magnitude of the return loss is also very good, -12 dB for the input and -16.5 dB for the output. The achieved gain is also higher than the desired minimum; here, 17.7 dB was obtained instead of 16 dB.

One interesting observation is that the maximal gain (MSG - maximal stable gain) occurs at a different point than the minimum return loss. This is normal behavior that in a more complex design would be presented on a Smith chart using gain and stability circles. In such a Smith chart, the rotation does not indicate a change of the frequency axis; the circles indicate a boundary where certain conditions are maintained, and the plot is made for a single frequency point.

The used .s2p file did not include noise parameters, so I was not able to simulate noise circles for this circuit. However, using the gain method and a spectrum analyzer, I measured a noise figure of 3.68 dB. Not great by any means, but it is a good parameter to know. Lowering Ic and conducting a more in-depth analysis of noise circles could reveal a design with potentially worse return loss but better NF. In RF, you rarely get something for free; some compromises usually have to be made.

In conclusion, if you want a sure way of getting a working LNA, the MMIC is most likely the best choice if you value your sanity and time. If you want to learn something, then designing a BJT RF amplifier is a good challenge. I highly recommend designing at least one amplifier like this if you are an amateur radio operator or if you want to construct your own RF devices in the future.

I have also verified that the amplifier offers the best performance for the 10 V input voltage by performing a simple push/pull effect measurement, which shows the effect of supply voltage on S21, S11, and S22. It can be observed that the input voltage affects the S parameters, as proper matching is achieved for 10 V and 12 V, with only 10 V resulting in a global minimum exactly at 433 MHz.

In the future, I would like to revisit this project and measure its linearity in terms of IP3 and IMD3. Currently, I don't have a signal generator that can control the output power at that frequency, oh well...

sp6gk 'at' protonmail.com

Here is demonstration of a restored radio from 1938.

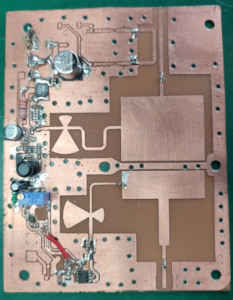

Almost assembled fully home made 2.4 GHz power amplifier on LDMOS transistor.

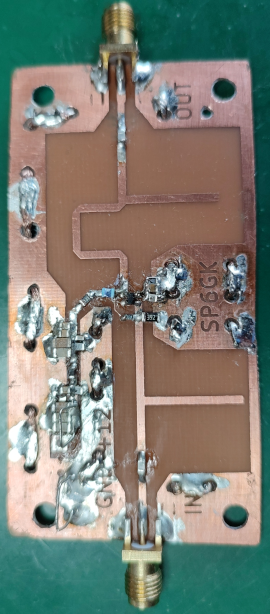

1.25 GHz small signal amplifier with open stub matching. Active element is BFP420 BJT.

My 120 cm prime focus dish. For now in the feed I have the Bullseye LNB. Thanks to my home made bias Tee and polarization controller I can receive the QO-100 satelite just fine on the RTL-SDR. Now I am working on upconverter and 2.4 GHz PA for the uplink.